State S3: The Multiplication is complete and the next state is S0. – In each cases, the Multiplier and the Product registers are shifted. State S2: If the loop counter saturates (overflow after an increment) we continue to state S3, otherwise we return to state S1. – The ALU result is loaded in the Product register. State S1: The next state is always S2. – The Product register and the loop counter are initialized to 0. State S0: We wait until the start signal is active on the rising edge of the clock before going into state S1 and initializing the registers where: – The Multiplicand and Multiplier registers load the input values. The reset signal resets the state machine to state S0. end_counter shift_product shift_multiplier start -Įnd_counter shift_product shift_multiplier It includes a 3-bit saturating counter used to count the 8 steps of the addition algorithm. The system Controller: – It contains a state machine, and it sets the control signals of all the components.Ĥ State machine The controller contains the following state machine. The 8-bit Adder: – It adds the result of the AND gates with the 8 most significant bits of the Product output. The AND gates: – It performs the AND logical operation on each Multiplicand bits with the least significant bit of the Multiplier. – The dataout output bits are its 16 least significant bits. – It shifts to the right when shift is high. – It loads the Add result in its most significant bits when load is high. The 17-bit shift-register Product: – It’s initialized to 0 when reset is high. – The dataout output is the least significant bit of the register. – It shifts to the right when shift right is high.

The 8-bit shift-register Multiplier: – Operand A is loaded when load is high.The 8-bit register Multiplicand: – Operand B is loaded when load is high.The components description is listed below.

The following figure describes the architecture of the multiplier. This algorithm is inspired from the multiplication method you learned at school: you sequentially multiply the multiplicand (operand B in the figure) by each digit of the multiplier (operand A in the figure), adding the intermediate results to the properly shifted final result. To implement the sequential multiplier, we will use the Shift-and-Add algorithm. Output done: synchronous signal that is set during 1 cycle by the multiplier when the result of the operation is available.Input start: synchronous signal that must be high to start a new operation.Input reset: asynchronous reset signal to initialize the system.

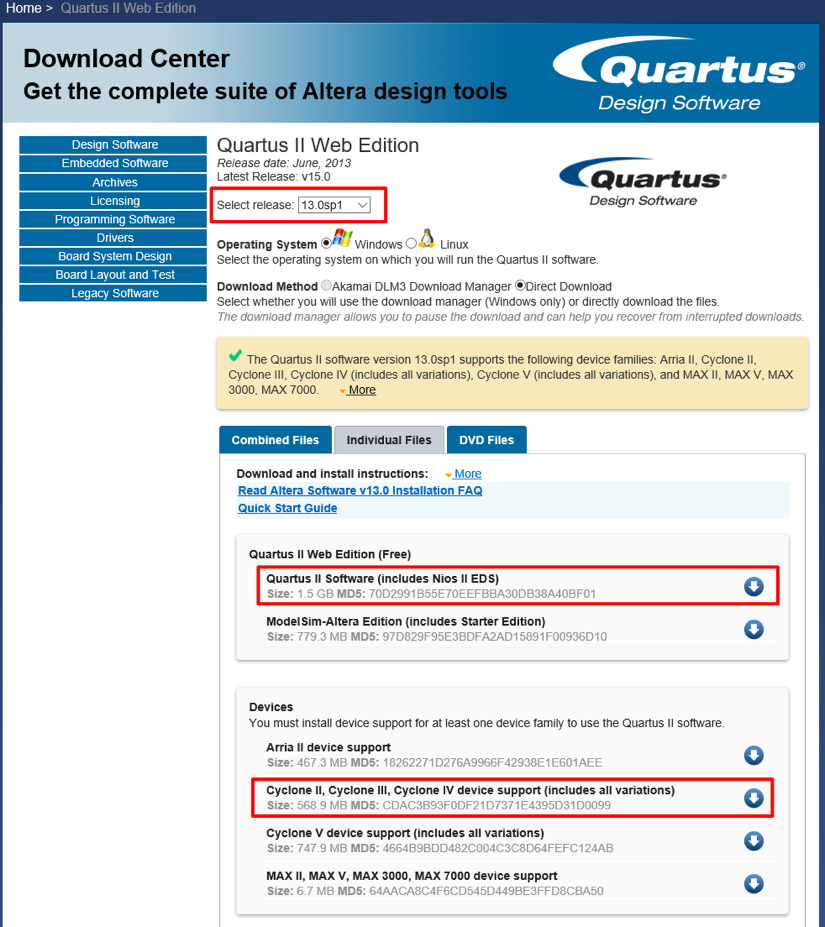

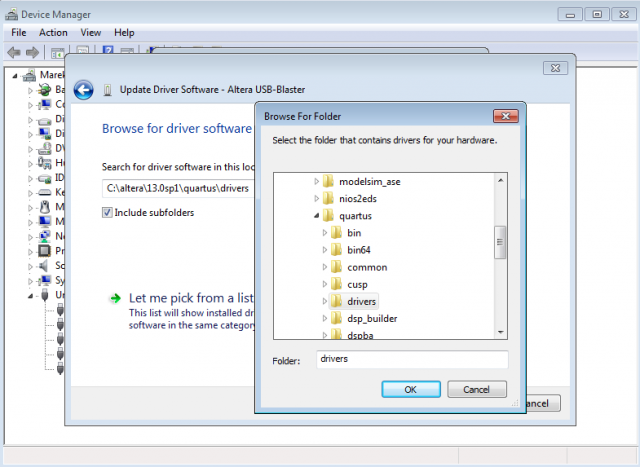

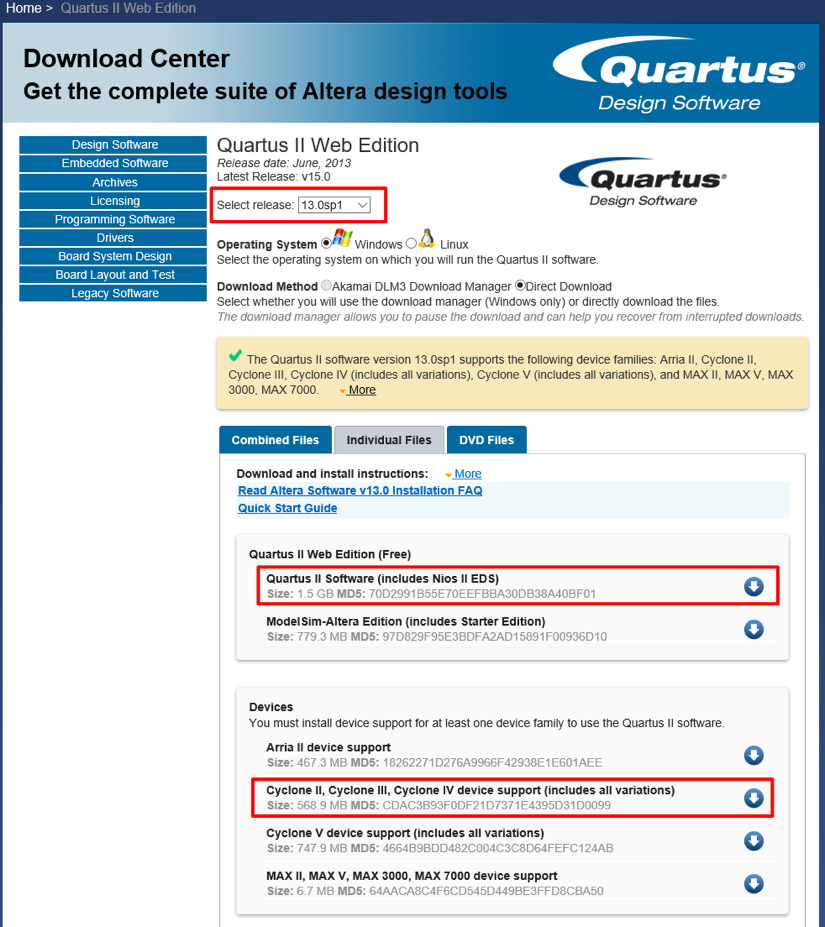

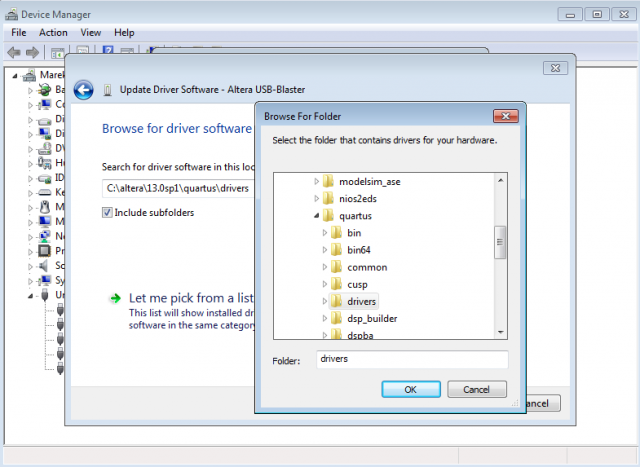

Input clk: clock signal to synchronize the system. Notice that the output bitwidth is the sum of the bitwidth of each input operand.ģ Sequential multiplier A sequential multiplier requires some additional signals for synchronization purpose. The next figure is the generic entity of a combinatorial multiplier. Quartus II Web Edition and ModelSim-Altera.ġ Introduction As a reintroduction to VHDL, you will implement a sequential multiplier using the Shift-and-Add algorithm.Ģ Binary multiplication Example of a 4-bit unsigned multiplication (11 × 9 = 99): Multiplicand Multiplier A 8-bit Sequential Multiplier Learning Goal: A Simple VHDL Design.

Input clk: clock signal to synchronize the system. Notice that the output bitwidth is the sum of the bitwidth of each input operand.ģ Sequential multiplier A sequential multiplier requires some additional signals for synchronization purpose. The next figure is the generic entity of a combinatorial multiplier. Quartus II Web Edition and ModelSim-Altera.ġ Introduction As a reintroduction to VHDL, you will implement a sequential multiplier using the Shift-and-Add algorithm.Ģ Binary multiplication Example of a 4-bit unsigned multiplication (11 × 9 = 99): Multiplicand Multiplier A 8-bit Sequential Multiplier Learning Goal: A Simple VHDL Design.

0 kommentar(er)

0 kommentar(er)